Register Buffer Terkendali & Register Geser Terkendali

1. Register Buffer Terkendali

Cara kerja dari rangkaian penyimpan data secara paralel :

Ketika Kendali Masukan diberi nilai "0", maka keluaran dari gerbang X selalu bernilai "1". Ini berarti bahwa sinyal Preset dan sinyal Preclear bernilai "1". Karena Preset dan Preclear dinyatakan aktif rendah, maka FF berfungsi normal. Namun karena clock bernilai nol, maka keluaran FF akan stabil (mempertahankan nilai semula). Dalam keadaan ini data lama ditahan, dan data baru tidak boleh masuk.

Ketika Kendali Masukan diberi nilai "1", maka keluaran seluruh gerbang X bergantung kepada data yang dimasukkan. Bila datanya "0", maka Ps = 1 dan Pc = 0 maka keluaran FF yang bersangkutan akan sama dengan "0" pula. Selanjutnya jika data yang masuk = 1, maka Ps = 0 dan Pc = 1 sehingga keluaran pada FF yang bersangkutan = 1. Ini berarti ketika Kendali Masukan bernilai "1", keluaran pada masing-masing FF akan sama dengan nilai data yang akan disimpan dan dapat dikatakan register dalam proses menyimpan data.

Ketika Kendali Masukan diberi nilai "0", maka keluaran dari gerbang X selalu bernilai "1". Ini berarti bahwa sinyal Preset dan sinyal Preclear bernilai "1". Karena Preset dan Preclear dinyatakan aktif rendah, maka FF berfungsi normal. Namun karena clock bernilai nol, maka keluaran FF akan stabil (mempertahankan nilai semula). Dalam keadaan ini data lama ditahan, dan data baru tidak boleh masuk.

Ketika Kendali Masukan diberi nilai "1", maka keluaran seluruh gerbang X bergantung kepada data yang dimasukkan. Bila datanya "0", maka Ps = 1 dan Pc = 0 maka keluaran FF yang bersangkutan akan sama dengan "0" pula. Selanjutnya jika data yang masuk = 1, maka Ps = 0 dan Pc = 1 sehingga keluaran pada FF yang bersangkutan = 1. Ini berarti ketika Kendali Masukan bernilai "1", keluaran pada masing-masing FF akan sama dengan nilai data yang akan disimpan dan dapat dikatakan register dalam proses menyimpan data.

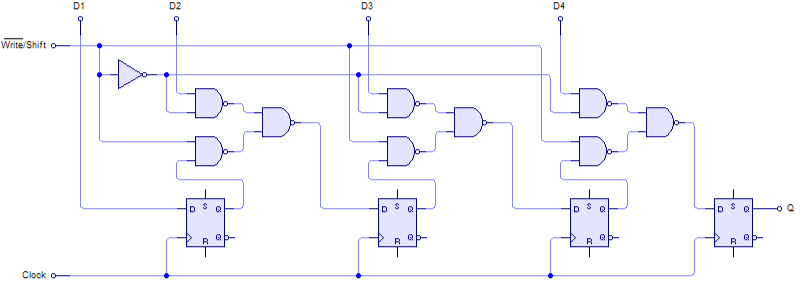

2. Register Geser Terkendali

Sebuah register geser terkendali (controlled shift register) mempunyai masukan-masukan kendali yang mengatur operasi rangkaian pada pulsa pendetak yang berikutnya.

Jika SHL rendah maka sinyal SHL tinggi. Keadaan ini membuat setiap keluaran flip-flop masuk kembali ke masukan datanya. Karena itu data tetap tersimpan pada setiap flip-flop pada waktu pulsa-pulsa detak tiba.

Jika SHL tinggi, Din akan masuk ke dalam flip-flop paling kanan, Q0 masuk ke dalam flip-flop kedua, Q1 masuk ke dalam flip-flop ketiga, dst. Dengan demikian rangkaian bertindak sebagai register geser kiri.

Pengisian seri (serial loading) berarti penyimpanan sebuah kata dalam register dengan cara memasukkan 1 bit pada tiap pulsa detak.

Tidak ada komentar:

Posting Komentar